The STM32H7A3/7B3 lines of microcontrollers include an Arm® Cortex®-M7 core (with double-precision floating point unit) running up to 280 MHz.

Performance

280 MHz fCPU

1414 CoreMark

599 DMIPS executing from Flash memory, with 0-wait states thanks to its L1 cache.

L1 cache (16 Kbytes of I-cache +16 Kbytes of D-cache) boosting execution performance from external memories.

Security

STM32H7B3 MCUs include the following additional security features:

Crypto/hash hardware acceleration

On-the-fly decryption on Octo-SPI external serial flash memory

Secure Firmware Install (SFI) embedded security services to authenticate and protect your software IPs while performing initial programming.

Secure Boot Secure Firmware Update (SBSFU)

Power efficiency

Dual-power domain architecture enables each power domain to be set in low-power mode to optimize power efficiency

Embedded SMPS to scale down the supply voltage. It can also be used to supply external circuitry and can also be combined with the LDO for specific use cases:

120 µA/MHz typical @ VDD = 3.3 V and 25 °C in Run mode (peripherals off) and SMPS

32 µA typical in STOP mode (low-power mode)

2.2 µA typical in Standby mode (low-power mode)

0.74 µA typical in VBAT mode with RTC (low-power mode)

Graphics

LCD-TFT controller interface with dual-layer support Chrom‑ART Accelerator™ boosts graphical content creation while saving core processing power, thus freeing up the MCU for other application needs Chrom-GRC™ optimizes RAM use JPEG hardware accelerator for fast JPEG encoding and decoding, off-loading the CPU

Embedded peripherals

Up to 35 communication interfaces including FD-CAN, USB 2.0 high-speed/full-speed, camera interface, Parallel synchronous data input/output slave interface (PSSI) Easily extendable memory range using the flexible memory controller with a 32-bit parallel interface, or the dual Octo-SPI serial Flash memory interface

Analog: Dual 16-bit ADCs Multiple 16- and 32-bit timers running at up to 280 MHz

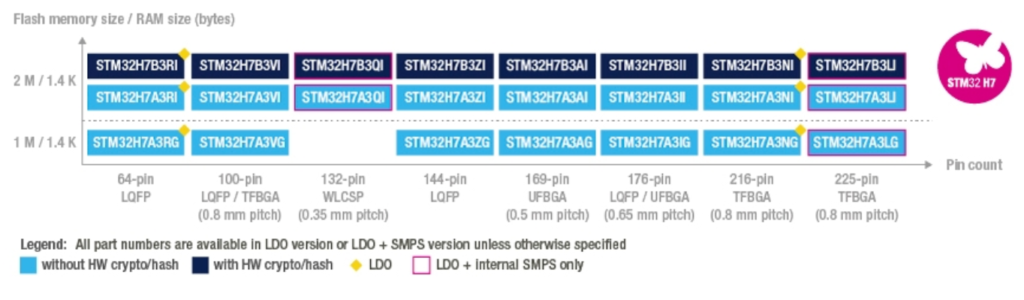

The STM32H7A3/7B3 MCU lines provides 1 to 2 Mbytes Flash memory, 1.4 Mbytes of SRAM