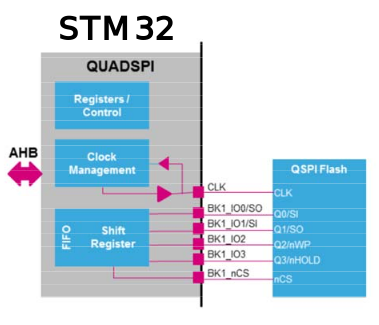

The QUAD SPI (QSPI) interface permits to connect external compact-footprint and high-speed memories.

QSPI memory to be seen as an internal memory.

Allows code execution (XIP mode) from QSPI Flash memory.

Supports SIOO mode also named Continuous Read Mode by some memory manufacturers for higher execution performance.

QSPI support the Interrupts and DMA usage.

AN4760 application note describes the QSPI interface on the STM32 microcontrollers and explains how to use the module to configure, program, and read external QSPI memories.

It describes some typical use cases to use the QSPI interface based on some software examples from the STM32Cube firmware package and from the STM32F7 Series application notes.

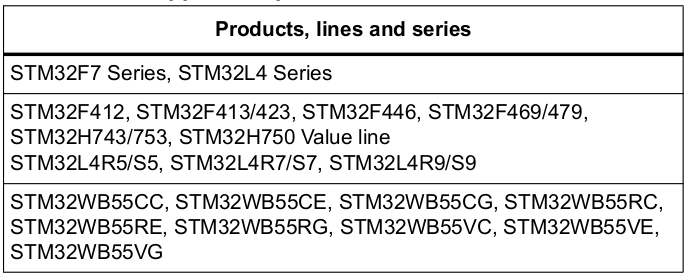

Below there is a list of the actual (Feb.2020) STM32 that support QSPI, please check the new ones on Internet.

QSPI benefits against classic SPI and parallel interfaces

The QSPI brings more performance in terms of throughput compared to classical SPI.

The classical SPI uses only one data line while the QSPI uses four data lines which multiplies the data throughput by almost four times.

Compared to FMC (flexible memory interface) and other parallel interfaces, QSPI permits the connection of a lower cost external Flash memory to small packages, reducing the PCB area, simplifying the PCB design and reducing the GPIOs (general-purpose input/output) usage.

In QSPI mode only six GPIOs are used: four lines for data plus one line for clock and another for chip select.

In Dual-Flash Quad-SPI mode only 10 GPIOs are used, amongst which eight lines are for data.

QSPI in a smart architecture

The QSPI interface is mapped on a dedicated layer on AHB allowing it to be accessible as an internal memory thanks to the Memory-mapped mode.

In addition, the QSPI is integrated in a smart architecture which allows the following features:

• Masters to access the external QSPI memory without any CPU intervention.

• Masters to read data from QSPI memory even in Sleep mode when the CPU is stopped

thanks to the STM32 smart architecture.

• CPU as a master can access QUADSPI and execute code from the memory.

• GP DMA to do transfer from QSPI to other internal or external memories.

• Graphical DMA2D to directly build RAM video frames using QSPI Flash.

Execute in place (XIP)

The prefetch buffer supports execution in place, therefore the code can be executed directly from the external QSPI memory.

The QSPI anticipates the next CPU access and loads in advance the byte at the following address.

If the subsequent access is indeed made at a continuous address, the access is completed faster since the value is already prefetched.

Booting from QSPI Flash memory

Boot from the QSPI memory is not supported but the user can boot from the internal Flash memory and then configure the QSPI in Memory-mapped mode and then the execution starts from the QSPI memory.

For more details on how to execute from the external QSPI memory, refer to AN4760 Section 5.2 on page 67.

Low-power modes

The STM32 power state is an important requirement that must be considered as it has a

direct effect on the QSPI interface state.

For example, if the MCU is in Standby mode then the QSPI has to be reconfigured after wakeup from this mode.

Note:

The QSPI memories can also be put in low-power mode. Depending on the memory brand, some devices support both Standby mode and Deep power-down mode while other devices support only Standby mode.

In order to save more energy when the application is in low-power mode, it is recommended to put the QSPI memory in low-power mode before entering the STM32 in low-power mode.

More information on reducing power consumption is available on AN4760 Section 6.2 on page 90.

It is possible to perform transfers in Sleep mode while the CPU is stopped thanks to the

STM32 smart architecture and to the fact that in Sleep mode all peripherals can be enabled. This can fit wearable applications where the low-power consumption is a must.

An AHB master such as DMA could continue the transfers from the QSPI (when

Memory-mapped mode is used) even after entering the MCU in Sleep mode.

Once the transfer is completed an interrupt can be generated to wakeup the STM32.

Refer to the products reference manuals for low-power mode configuration details.

LINK

- STM32L4 QSPI presentation is here

- STM32L4 video training: 02.9 System and memories – QSPI memory controller theory is here

- STM32WB QSPI presentation is here

- STM32G4 QSPI presentation is here

- AN5156 Introduction to STM32 microcontrollers security is here

- Protecting microcontrollers. Implementing Firmware Hardening and Secure Boot on STM32 is here

- STM32H7A3/7B3 lines include the On-the-fly decryption on Octo-SPI external serial flash memory

- STM32L5 line in some package include the On-the-fly decryption on Octo-SPI external serial flash memory, see for example the STM32L562xx

- Video concerning the STM32L5 OLT – 30 – Security On The Fly Decryption Engine OTFDEC is here